9.3 VM as a Tool for Caching(캐싱 도구로서의 VM)

결론짓자면, VM은 디스크에 저장된 N개의 바이트 크기의 셀 배열로 구성됨.

- 각 바이트는 특정 가상주소를 가지며, 배열의 인덱스로 작용함.

- 디스크 안의 배열 정보는 메인 메모리에 캐시됨.

- 메모리 계층구조 안에 있는 캐시는 블록 단위로 분할되며, 디스크와 메인 메모리 사이의 징검다리 역할을 해줌.

- VM system은 가상메모리를 규정된 사이즈 블록 단위로 분할하여 관리함. 이 분할된 블록을 가상페이지라고 부른다.

- 각 가상 페이지는 $P = 2^p$바이트의 크기를 가짐. 물리 메모리도 물리 페이지로 분할되어 사용된다.

가상페이지의 집합은 세개의 독립된 부분집합으로 이루어진다.

- Unallocated : VM 시스템에 의해 아직까지 할당되지 않은 페이지들. 비할당된 블록들은 이들과 관련된 데이터를 하나도 가지고 있지 않으며, 따라서 디스크 상에 어떠한 공간도 차지하지 않는다.

- Cached : 현재 물리 메모리에 캐시되어 할당된 페이지들.

- Unchaced : 물리 메모리에 캐시되지 않은 할당된 페이지들.

9.3.1 DRAM Cache Organization (DRAM 캐시의 구성)

메모리 계층구조 내의 서로 다른 캐시간의 질서를 바로잡기 위해, CPU와 메인 메모리 사이에서 L1, L2, L3 캐시 메모리를 말하기 위해 SRAM 캐시라는 용어를 정의할 것이다.

또한 가상페이지를 메인 메모리로 캐싱하는 VM 시스템캐시를 말하기 위해 DRAM캐시라는 용어를 정의할 것이다.

메모리 계층구조 내에서 DRAM캐시의 위치는 이들이 구성된 방식에 큰 영향을 가진다.

- DRAM이 SRAM보다 약 10배 느리며, 디스크는 DRAM보다 100000배 느림.

DRAM 캐시 미스는 SRAM 캐시미스에 비해 코스트가 비싸다.

- DRAM캐시미스는 디스크에서 처리되지만 SRAM 캐시미스는 DRAM 기반 메인 메모리로부터 지원받기 때문이다.

- 디스크 섹터로부터 첫번째 바이트를 읽는 비용은 섹터에서 연속적인 바이트를 읽는 것 보다 약 100000배 느리다.

큰 규모의 미스 비용과 첫 번째 바이트를 접근하는데 드는 비용 때문에 가상 페이지는 커지고 있으며, 대개 4KB에서 2MB까지 값을 가진다.

DRAM 캐시는 완전 결합성이다. → 모든 가상 페이지는 물리 페이지에 둘 수 있다.

미스 발생 시 교체 정책은 더 큰 중요성을 가정하는데, 잘못된 가상페이지를 교체하는 것과 관련된 비용이 매우 높기 때문이다.

그래서 운영체제는 하드웨어가 SRAM 캐시에 대해서 처리하는 것 보다 훨씬 복잡한 DRAM 캐시를 위한 교체 알고리즘을 사용한다.

DRAM은 항상 write-through 대신 write-back을 사용한다.

9.3.2 Page Tables (페이지 테이블)

- 모든 캐시에서처럼 VM 시스템은 가상 페이지가 DRAM 어딘가에 캐시되었는지 결정하기 위한 방법을 갖고 있어야 한다. 그렇다면, 이 시스템은 어떤 물리페이지를 캐싱했는지 결정해야 한다.

- 만일 미스가 존재한다면 시스템은 디스크 어디에 가상페이지가 저장되어있는지 결정해야하며, 물리 메모리 중 희생자 페이지를 선택해야하고, 가상페이지를 디스크에서 DRAM으로 복사해서 희생자 페이지를 교체한다.

- 이런 기능은 OS와 MMU 내의 주소 번역 하드웨어, 가상페이지를 물리 페이지로 매핑하는 페이지 테이블이라고 알려진 물리 메모리에 저장된 자료구조의 조합으로 제공된다. 주소 번역 하드웨어는 이들이 가상 주소를 물리주소로 변환할때마다 페이지 테이블을 읽는다. 운영체제는 페이지 테이블의 콘텐츠 관리와 페이지들을 디스크와DRAM 사이에서 왔다리갔다리를 관장한다.

- 페이지테이블은 페이지 테이블 엔트리라는 구조의 배열이며, VM의 각 페이지는 페이지 테이블 내에 고정된 오프셋 위치에 PTE를 갖는다.

- 편의상 PTE가 한개의 유효비트, n비트의 주소 필드로 구성된다고 가정하자.

- 유효비트는 가상 페이지가 현재 DRAM에 캐시되어있는지를 나타낸다. 만일 유효비트가 세팅되었다면 주소필드는 가상 페이지가 캐시되어 대응되는 DRAM의 물리페이지의 시작을 나타낸다.

- 그렇지 않다면 NULL주소는 가상페이지가 아직 할당되지 않았음을 나타낸다.

9.3.3 Page Hits (페이지 적중)

- CPU가 DRAm에 캐시되어있는 가상메모리의 VP2워드 한개를 읽을 때 어떤 일이 발생하는지 생각해보자.

- 주소 번역 하드웨어는 PTE2를 찾기 위해서 인덱스로 가상주소를 사용하고, 이것을 메모리에서 읽는다. 유효비트가 세트되어있기 때문에 주소 번역 하드웨어는 VP 2가 메모리에 캐시되어있다는 것을 알고있다. 그래서 PTE 내의 물리 메모리 주소를 사용해서 해당 워드의 물리 주소를 구성한다.

9.3.4 Page Faults (페이지 오류)

- DRAM 캐시 미스는 흔히 페이지 오류라고 알려져있다.

- CPU는 DRAM에 캐시되어있지 않은 VP3 내의 워드를 참조한다.

- 주소 번역 하드웨어는 메모리에서 PTE3를 읽으며 VP3가 캐시되어있지 않다는 것을 유효비트로부터 유추해서 페이지 오류 예외를 유발시킨다.

- 페이지 오류 예외는 커널 내에 페이지 오류 예외 핸들러를 호출해 victim 페이지인 PP3에 저장된 VP4를 선택한다. VP4가 변경되었다면 커널은 이것을 다시 디스크에 복사한다.

- 어느 경우든지 간에 커널은 VP4에 대한 페이지 테이블 엔트리를 수정해서 VP4가 더이상 메모리에 캐시되지 않았다는 사실을 반영한다.

- 다음으로 커널은 VP3를 디스크에서 메모리 내의 PP3로 복사하고 PTE3를 갱신하고 그 후에 리턴한다. 핸들러가 리턴할 때 오류 인스트럭션을 재시작하고, 이것은 오류 가상주소를 주소 번역 하드웨어로 재전송한다.

- 이때는 VP3가 메인 메모리에 캐시되어있으며 페이지 적중은 정상적으로 주소 번역 하드웨어에 의해 처리된다. 그림 9.7은 페이지 적중 후의 예제 페이지 테이블의 상태를 보여준다.

9.3.5 Allocating Pages (페이지 할당)

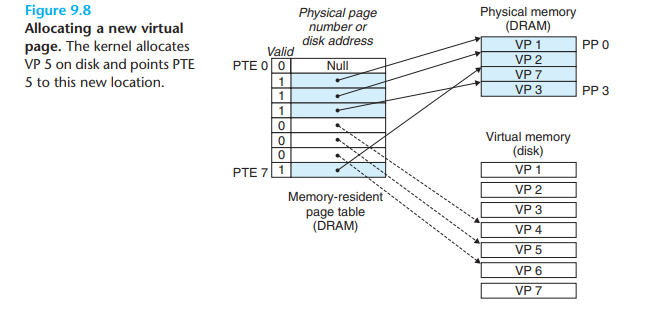

- 위 그림 9.8은 운영 체제가 malloc 호출의 결과로 가상 메모리의 새 페이지를 할당할 때 예제 페이지 테이블에 미치는 영향을 보여준다.

- 이 예에서 VP 5는 디스크에 공간을 생성하고 디스크에 새로 생성된 페이지를 가리키도록 PTE 5를 업데이트하여 할당된다.

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [CSAPP] 8.3 System Call Error Handling (시스템 콜 에러 처리) (0) | 2023.03.01 |

|---|---|

| [CSAPP] 8.2 Processes (프로세스) (0) | 2023.03.01 |

| [CSAPP] 9.2 Address Spaces(주소 공간) (0) | 2023.03.01 |

| [CSAPP] 9.1 Physical and Virtual Addressing(물리 및 가상주소 방식) (0) | 2023.03.01 |

| [CSAPP] 9.6 Address Translation(주소 변환) (0) | 2023.03.01 |

![[CSAPP] 9.3 VM as a Tool for Caching(캐싱 도구로서의 VM)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbfQ7ld%2Fbtr06V54pSb%2FAAAAAAAAAAAAAAAAAAAAAMl3WLIxFwsiBLl4EqsLPIiI-b3vQfRtOH2yCvLDkfBk%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1759244399%26allow_ip%3D%26allow_referer%3D%26signature%3D013V%252BTiCwbx%252Fbu3oMU281LlKbPA%253D)